La producción de chips de 2 nm de TSMC podría comenzar en 2025 para los iPhone 18 Pro

TSMC supera expectativas en la producción de chips de 2 nm, posicionándose para suministrar tecnología avanzada en los iPhone 18 Pro de 2026.

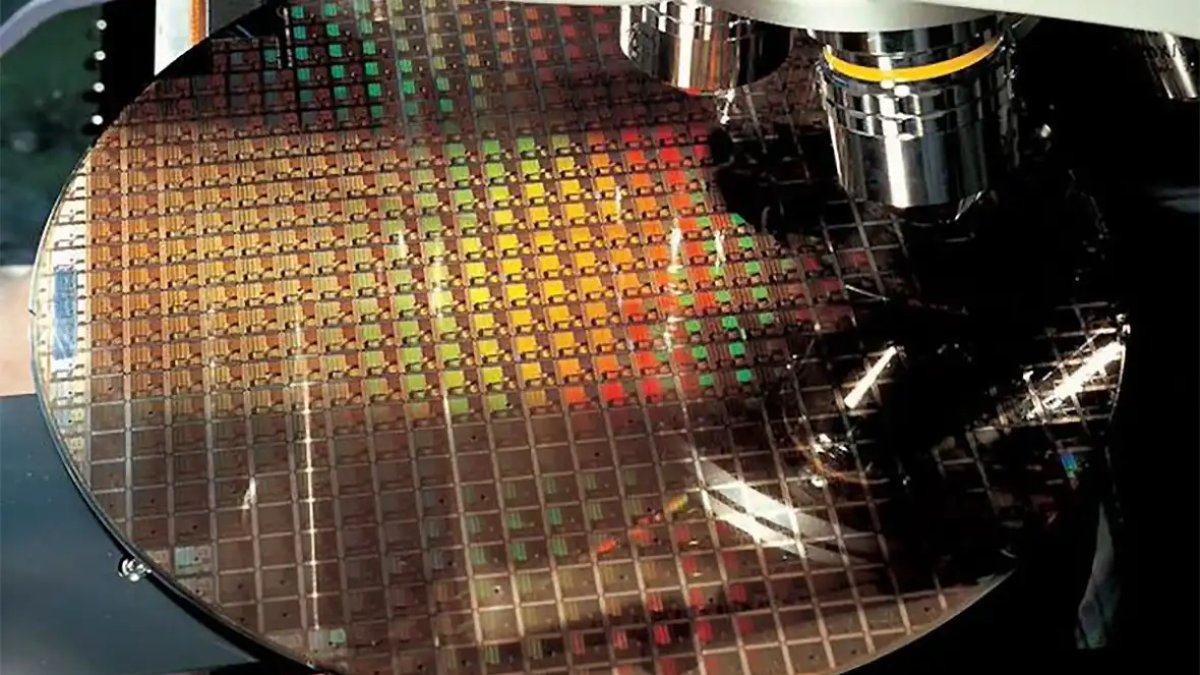

TSMC ha logrado resultados por encima de lo esperado en la producción de prueba de su tecnología de chips de 2 nanómetros, alcanzando una tasa de rendimiento superior al 60%, según fuentes del mercado taiwanés. Esto sugiere que la compañía está en una posición sólida para iniciar la producción masiva de chips de 2 nm en 2025, que se espera sean utilizados en los modelos de iPhone 18 Pro de Apple en 2026.

El fabricante de semiconductores está llevando a cabo la producción de prueba en su fábrica de Baoshan en Hsinchu, donde ha implementado una nueva arquitectura denominada 'nanosheet'. Esta tecnología representa un avance significativo en comparación con el actual proceso de 3 nm FinFET. Se proyecta que TSMC trasladará esta experiencia de producción a su planta en Kaohsiung para iniciar la fabricación masiva.

Los recientes informes de analistas, incluido el de Ming-Chi Kuo, sugieren que los iPhone 18 Pro de 2026 utilizarán exclusivamente chips producidos bajo el proceso de 2 nm de TSMC, y que contarán con 12 GB de RAM. Por el contrario, los modelos estándar de iPhone 18 seguirán utilizando el procesador de 3 nm mejorado debido a consideraciones de costo.

Se prevé que el proceso de 2 nm capte considerable interés, especialmente del sector de la inteligencia artificial. El CEO de TSMC, C.C. Wei, ha señalado una demanda inesperadamente alta para esta tecnología, lo que sugiere que la producción masiva se acelerará tan pronto como sea posible para satisfacer dicha demanda.

Además, TSMC tiene planes de introducir un nuevo proceso denominado A16 en 2026, que combinará la arquitectura Super Power Rail con transistores 'nanosheet'. Este avance podría ofrecer un incremento del 8% al 10% en el rendimiento manteniendo el mismo voltaje y complejidad, así como una reducción del consumo energético de entre el 15% y el 20% a la misma frecuencia. Asimismo, se espera un aumento en la densidad del empaque de los transistores en los núcleos de procesamiento de entre el 7% y el 10%, dependiendo del diseño.